Category: PhD

-

Graduated with a PhD on 8th April 2022 from Trinity College Dublin

Graduated today with a PhD in Computer Science from Trinity College Dublin, Ireland. Hard to believe it, but I am now officially Dr James Garland, PhD!

-

Postgraduate Researcher Required

I am looking for a potential Postgraduate Researcher interested in machine learning, digital twins, and energy efficiency for a President’s Research Fellowship Scholarship position based at the Institute of Technology Carlow, Carlow, Ireland. Project Abstract: https://www.itcarlow.ie/public/userfiles/files/13-Calibration-Digital-Twins-Buildings-using-Machine-Learning-v2.pdf Funding Details: https://www.itcarlow.ie/research/post-graduate-studies/graduate-opportunities/presidents-research-fellowship-scholarship.htm Please send you applications or contact me for more details at my email: james.garland@itcarlow.ie

-

PhD Thesis now Open-Sourced online and in TCD Library

My PhD thesis is now available in the online open-sourced Trinity’s Access to Research Archive (TARA) and physically in the Trinity College Dublin library. You can read the online version from TARA or the School of Computer Science and Statistics repositories.

-

I passed my PhD Viva yesterday

Delighted to say that I passed my PhD Viva yesterday after a 3.5-hour viva examination. With thanks to my examiners Dr Georgios Karakonstantis and Dr Michael Manzke and chaired by Prof Khurshid Ahmad. And a special thanks to my adviser Prof. David Gregg. It’s been a blast! And a big, big thanks for the love […]

-

The Next Platform Interviewed me about HOBFLOPS CNNs

-

I’ve co-written a chapter of Many-Core Computing: Hardware and Software book.

I’m delighted to announce that the book “Many-Core Computing: Hardware and Software” has been published today by the Institution of Engineering and Technology (IET). I, along with Dr. Andrew Anderson, Dr. YuanWen, Barbara Barabasz, Kaveena Persand, Dr. Aravind Vasudevan, and Dr. David Gregg have written chapter 6 entitled “Hardware and software performance in deep learning”. […]

-

PASM Paper presented at HiPEAC2019

And that’s the PASM paper presented. Lots of interest and very good questions from the audience and the session chair Luca Fanucci (Università di Pisa @Unipisa). Thoroughly enjoyed it. #HiPEAC19#hipeac2019

-

Come and see my talk at HiPEAC 2019

Come and see my talk at HiPEAC 2019 about my second PhD published paper.

-

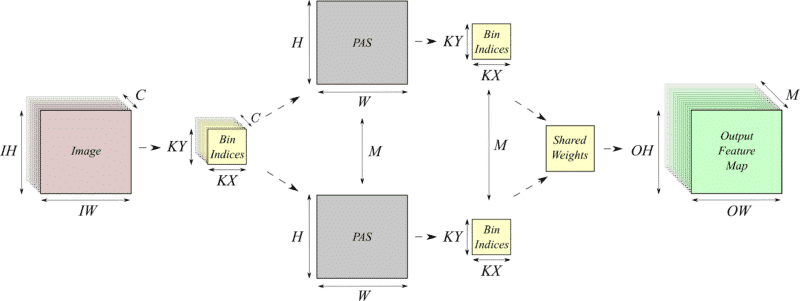

Second Ph.D. Paper Published by ACM TACO

Convolutional neural networks (CNNs) are one of the most successful machine learning techniques for image, voice and video processing. CNNs require large amounts of processing capacity and memory bandwidth. Hardware accelerators have been proposed for CNNs which typically contain large numbers of multiply-accumulate (MAC) units, the multipliers of which are large in an integrated circuit (IC) gate count and power consumption. “Weight sharing” accelerators have been proposed where the full range of weight values in a trained CNN are compressed and put into bins and the bin index used to access the weight-shared value. We reduce power and area of the CNN by implementing parallel accumulate shared MAC (PASM) in a weight shared CNN. PASM re-architects the MAC to instead count the frequency of each weight and place it in a bin. The accumulated value is computed in a subsequent multiply phase, significantly reducing gate count and power consumption of the CNN. In this paper, we implement PASM in a weight-shared CNN convolution hardware accelerator and analyze its effectiveness. Experiments show that for a clock speed 1GHz implemented on a 45nm ASIC process our approach results in fewer gates, smaller logic, and reduced power with only a slight increase in latency. We also show that the same weight-shared-with-PASM CNN accelerator can be implemented in resource-constrained FPGAs, where the FPGA has limited numbers of digital signal processor (DSP) units to accelerate the MAC operations.

-

Passed My PhD Confirmation Viva

I undertook my Ph.D. Confirmation viva voce today (6th Feb 2018). This entailed a presentation and a report to two professors, Dr. Jonathan Dukes (presentation chair) and Dr. Michael Manzke (domain expert) of Trinity College Dublin who questioned me during and after the presentation. After a short discussion with my supervisor Dr. David Gregg, they […]